# **INTEGRATED CIRCUITS**

# P87LPC76x Low Pincount Microcontrollers

**Programming Specifications**

1999 Feb 18

#### 1. PINOUT

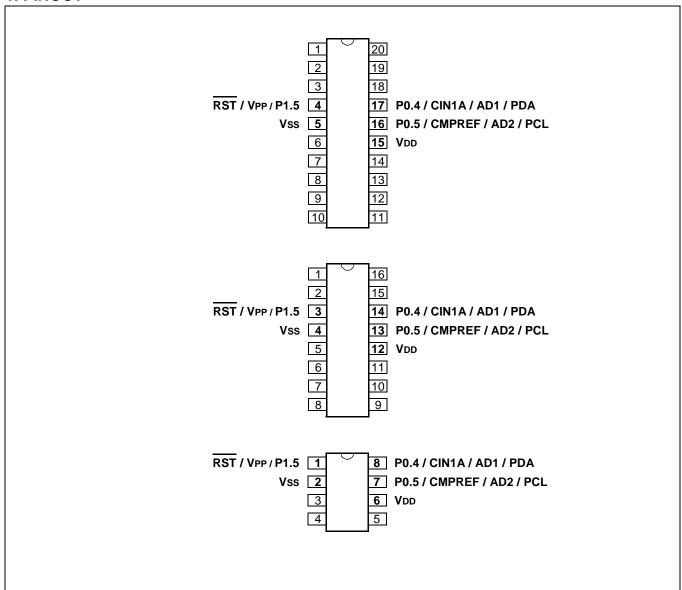

Figure 1: 20, 16, 8 pins DIP pinout

The 20 pin SO package outlines SOT163-1 is attached at the end of this document.

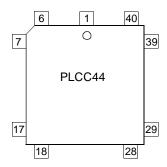

Figure 2: 44 pins PLCC bondout chip

| <u>Pin</u> | <u>FUNCTION</u> | <u>Pin</u> | <b>FUNCTION</b>     |

|------------|-----------------|------------|---------------------|

| 1          | VSS             | 44         |                     |

| 2          |                 | 43         |                     |

| 3          |                 | 42         |                     |

| 4          |                 | 41         |                     |

| 5          |                 | 40         |                     |

| 6          |                 | 39         |                     |

| 7          |                 | 38         | P0.4/CIN1A/AD1/PDA  |

| 8          | P1.5/RST/VPP    | 37         | P0.5/CMPREF/AD2/PCL |

| 9          |                 | 36         |                     |

| 10         | VSS             | 35         |                     |

| 11         |                 | 34         |                     |

| 12         |                 | 33         |                     |

| 13         |                 | 32         |                     |

| 14         |                 | 31         | VDD                 |

| 15         |                 | 30         |                     |

| 16         |                 | 29         |                     |

| 17         |                 | 28         |                     |

| 18         |                 | 27         |                     |

| 19         |                 | 26         |                     |

| 20         |                 | 25         |                     |

| 21         |                 | 24         |                     |

| 22         |                 | 23         | VDD                 |

|            |                 |            |                     |

Table 1: 44 PLCC pinout (programming related pins are in bold text)

#### 2. PIN DESCRIPTIONS

| MNEMONIC | 44 pins<br>package | 20 pins<br>package | 16 pins<br>package | 8 pins<br>package | TYPE | NAME AND FUNCTION                                               |

|----------|--------------------|--------------------|--------------------|-------------------|------|-----------------------------------------------------------------|

|          | PIN NO.            | PIN NO.            | PIN NO.            | PIN NO.           |      |                                                                 |

| VSS      | 10, 1              | 5                  | 4                  | 2                 | Р    | Ground: 0V reference.                                           |

| VDD      | 23, 31             | 15                 | 12                 | 6                 | Р    | Power Supply: 5V +/5V                                           |

| PCL      | 37                 | 16                 | 13                 | 7                 | Ì    | Serial clock input for EPROM programming communication.         |

| PDA      | 38                 | 17                 | 14                 | 8                 | I/O  | Serial data I/O for EPROM programming communication.            |

| VPP      | 8                  | 4                  | 3                  | 1                 | Р    | $V_{PP} = 10.75V +/- 0.25V$ $I_{PP} = 30mA$ during programming. |

Table 2: Programming pins in different packages

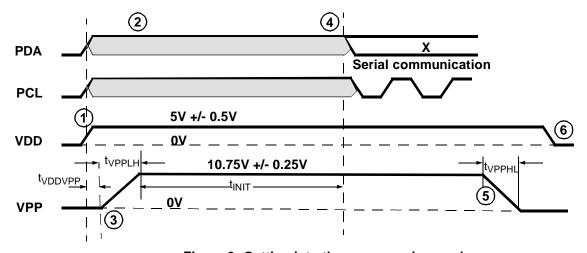

#### 3. GETTING INTO THE SERIAL PROGRAMMING MODE

- 1. Disconnect pins PCL and PDA.

- 2. Connect VDD; the part does not support "hot insertion" into the programming socket

- 3. Wait 20 uSec (Min) and raise  $V_{PP}$  to 10.75V +/- 0.25V;  $V_{PP}$  rise time is 1uSec to 100 uSec.

At this point the part is in the programming mode.

- 4. Wait t<sub>INIT</sub> = 60 uSec (Min) before beginning the serial communication to the part.

- 5. Get out of the programming mode by connecting  $V_{PP} = 0V$ ;  $V_{PP}$  fall time is 1uSec to 100 uSec.

- 6. Disconnect VDD before removing the part from the socket.

The programming mode enables the internal RC oscillator.

During the programming mode PDA and PCL pins are Schmitt trigger inputs.

Figure 3: Getting into the programming mode

| $VDD = 4.5V \text{ to } 5.5V; V_{PP} = 10.75V +/- 0.25$ | $V I_{PP} = 30 \text{mA during programming};$ | $T_{amb} = 10^{\circ}C \text{ to } +40^{\circ}C$ |

|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|

|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 0)/11001            |        |                                                                   | LIN |     |      |

|---------------------|--------|-------------------------------------------------------------------|-----|-----|------|

| SYMBOL              | FIGURE | PARAMETER                                                         | MIN | MAX | UNIT |

| t <sub>VDDVPP</sub> |        | V <sub>DD</sub> HIGH to V <sub>PP</sub> rising edge               | 20  |     | us   |

| t <sub>VPPLH</sub>  |        | V <sub>PP</sub> rise time                                         | 1   | 100 | us   |

| t <sub>VPPHL</sub>  |        | V <sub>PP</sub> fall time                                         | 1   | 100 | us   |

| t <sub>INIT</sub>   |        | V <sub>PP</sub> = 10.75V to the beginning of serial communication | 60  |     | us   |

**Table 3: Programming mode timings**

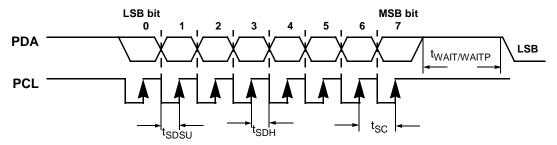

#### 4. PROGRAMMING MODE

The programming commands are sent by the programmer through the PCL and PDA lines.

Each programming command is one byte shifted into the part by 8 clocks.

The serial interface is identical to the 51's 8-bit serial UART mode 0; LSB is the first bit in the serial byte.

PCL pin is the clock input from the programmer.

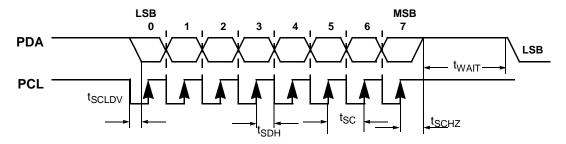

PDA pin is the data I/O. Data is enabled on the falling edge of PCL, and is clocked on the rising edge of PCL.

Data output from the part is disabled after the rising edge of PCL for the last bit in a data byte.

Figure 4: Writing programming commands by the programmer

| NAME       | OPCODE | FUNCTION                                                                        |

|------------|--------|---------------------------------------------------------------------------------|

| NOP        | 00H    | Not used                                                                        |

| LOAD_DATA  | 02H    | Load address counter with the next data byte                                    |

| RD_DATA    | 04H    | Read data byte addressed by the program counter                                 |

| INC_ADDR   | 06H    | Increment address counter                                                       |

| LD_ADRR_LO | 08H    | Load 8 LOW address bits into programming counter                                |

| LD_ADRR_HI | 0AH    | Load 8 HIGH address bits into programming counter                               |

| STRT_PRGM  | 0CH    | Start programming a data byte; always followed by the Stopt programming command |

| STP_PRGM   | 0EH    | Stop programming a data byte; always follows the Start programming command.     |

**Table 4: Programming commands**

#### Notes:

Wait 2 uSec between any two programming commands (except "Start Programming" to "Stop Programming") Wait 250uSec between "Start Programming" and "Stop Programming" commands.

## Example of a sequence of programming commands

| LD_ADDR_LO | Wait 2uSec   |

|------------|--------------|

| XX DATA    | Wait 2uSec   |

| LD_ADDR_HI | Wait 2uSec   |

| XX DATA    | Wait 2uSec   |

| LOAD_DATA  | Wait 2uSec   |

| XX DATA    | Wait 2uSec   |

| READ_DATA  | Wait 2uSec   |

| XX DATA    | Wait 2uSec   |

| INC_ADDR   | Wait 2uSec   |

| LOAD_DATA  | Wait 2uSec   |

| XX DATA    | Wait 2uSec   |

| STRT_PRGM  | Wait 250uSec |

| STP_PRGM   | Wait 2uSec   |

|            |              |

Table 5: Sequence of programming commands

Figure 5: Reading data by the programmer

| 0)/117.01          |        |                                                                 | LIN | IITS |      |

|--------------------|--------|-----------------------------------------------------------------|-----|------|------|

| SYMBOL             | FIGURE | PARAMETER                                                       | MIN | MAX  | UNIT |

| t <sub>SC</sub>    | 5      | Serial clock cycle time                                         | 0.2 | 1000 | us   |

| t <sub>WAIT</sub>  | 5      | Wait between two serial bytes                                   | 2   |      | us   |

| t <sub>WAITP</sub> | 5      | Wait after a "Start Programming" command                        | 250 |      | us   |

| t <sub>SDSU</sub>  | 4      | Serial data setup time to the rising edge of the serial clock   | 40  |      | ns   |

| t <sub>SDH</sub>   | 5      | Serial data hold time after the rising edge of the serial clock | 10  |      | ns   |

| t <sub>SCLDV</sub> | 5      | Serial clock LOW to valid data of the first data bit in a byte  |     | 40   | ns   |

| t <sub>SCHZ</sub>  | 5      | Serial clock HIGH to data Hi-Z at the last data bit in a byte   |     | 40   | ns   |

**Table 6: Programming commands timing**

| Address        | Memory Definition                                                  |

|----------------|--------------------------------------------------------------------|

| 0000H to 0FFFH | User's code; program/read by the programmer                        |

| FC30H          | Company signature 15H - Read only by programmer                    |

| FC31H          | Part's signature DDH - Read only by the programmer                 |

| FC60H          | Derivative's signature 00H - Read only by the programmer           |

| FCE0H to FCFFH | 32 bytes used as user's parameters; program/read by the programmer |

| FD00H          | User Configuration Reg. #1 (UCFG1) program/read by the programmer  |

| FD01H          | User Configuration Reg. #2 (UCFG2) program/read by the programmer  |

#### **Table 7: EPROM Mapping**

The programmer programs the user's code at address 0 to FFFH and configuration registers located at address FCE0H to FD01H. These configuration registers configure the chip's modes of operation.

#### 5. USER CONFIGURATION REG. #1 (UCFG1) AT ADDRESS FD00H

|                 | 7    | 6   | 5    | 4     | 3    | 2     | 1     | 0     |

|-----------------|------|-----|------|-------|------|-------|-------|-------|

| Programmed bits | WDTE | RPD | PRHI | BO2.5 | CLKR | FOSC2 | FOSC1 | FOSC0 |

| Erased State    |      |     |      |       | FFH  |       |       |       |

Table 8: User Configuration Register #1

WDTE: WatchDog Timer Enable;

1 = (Erased) WDT enabled

0 = (Programmed) WDT disabled

RPD: Reset Pin Disable;

1(Erased) External Reset pin disabled (The internal power-on reset is enabled)

0 (Programmed) External Reset pin enabled

PRHI: Port Reset High;

1 = Enable ports to high during and after RESET

0 = Enable ports to low during and after RESET

BO2.5: Brown out at 2.5V;

1 = Enable brown out at 2.5V

0 = Enable brown out at 3.8V

CLKR: CLock Rate select:

1 = Enable divide by 1 of clock (6 clocks per machine cycle)

0 = Enable divide by 2 of clock (12 clocks per machine cycle)

FOSC2 - FOSC0: Oscillator control bits;

|                                            | FOSC2 | FOSC1 | FOSC0 |

|--------------------------------------------|-------|-------|-------|

| External clock input at pin X1             | 1     | 1     | 1     |

| Internal RC clock; 6MHz +/- 25%            | 0     | 1     | 1     |

| 32KHz to 100KHz external Crystal/Resonator | 0     | 1     | 0     |

| 100KHz to 4 MHz external Crystal/Resonator | 0     | 0     | 1     |

| 4 MHz to 20 MHz external Crystal/Resonator | 0     | 0     | 0     |

Table 9: FOSC2-FOSC0 bit function

#### 6. USER CONFIGURATION REG. #2 (UCFG2 AT ADDRESS FD01H)

|                 | 7    | 6    | 5 | 4 | 3   | 2 | 1 | 0 |

|-----------------|------|------|---|---|-----|---|---|---|

| Programmed bits | SEC2 | SEC1 |   |   |     |   |   |   |

| Erased State    |      |      |   |   | FFH |   |   |   |

**Table 10: User Configuration Register #2**

SEC2-SEC1: SECurity bits 2 & 1;

- 11 = Security bits unprogrammed; Programming and Verify allowed.

- 10 = Security bit 2 unprogrammed; 1 programmed; Programming disabled, Verify enabled.

- 00 = Both bits programmed; Programming and Verify disabled

#### 7. 32 REGISTERS OF USER'S PARAMETERS (FCE0H TO FCFFH)

The 32 registers of user's parameters are programmed as code located at address FCE0H to FCFFH.

The content of the 32 parameter registers and the two configuration registers are defined by the HEX file at addresses:

| FCE0H to FCFFH | FCE0H to FCFFH 32 bytes used as user's parameters; program/read by the programmer |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|

| FD00H          | User Configuration Reg. #1 (UCFG1) program/read by the programmer                 |  |  |  |  |  |  |

| FD01H          | User Configuration Reg. #2 (UCFG2) program/read by the programmer                 |  |  |  |  |  |  |

The user should be able to display, edit, program and verify the two configuration registers and the user's 32 bytes located at address FCE0H to FCFFH.

# Package outlines

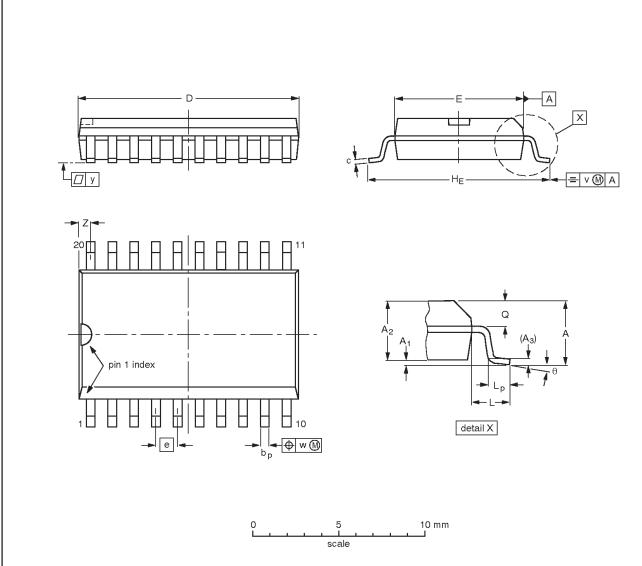

## SO20: plastic small outline package; 20 leads; body width 7.5 mm

SOT163-1

#### DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bр             | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q          | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|------|----------------|----------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 2.65      | 0.30<br>0.10   | 2.45<br>2.25   | 0.25 | 0.49<br>0.36   | 0.32<br>0.23   | 13.0<br>12.6     | 7.6<br>7.4       | 1.27  | 10.65<br>10.00 | 1.4   | 1.1<br>0.4     | 1.1<br>1.0 | 0.25 | 0.25 | 0.1   | 0.9<br>0.4       | 8° |

| inches | 0.10      | 0.012<br>0.004 | 0.096<br>0.089 | 0.01 | 0.019<br>0.014 | 0.013<br>0.009 | 0.51<br>0.49     | 0.30<br>0.29     | 0.050 | 0.419<br>0.394 | 0.055 | 0.043<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.035<br>0.016   | 0° |

#### Note

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

|  | OUTLINE  |        | REFER    | EUROPEAN | ISSUE DATE |            |                                  |

|--|----------|--------|----------|----------|------------|------------|----------------------------------|

|  | VERSION  | IEC    | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                       |

|  | SOT163-1 | 075E04 | MS-013AC |          |            |            | <del>-95-01-24</del><br>97-05-22 |

1997 May 22 35